|

專利國別 |

美國 |

發表日期 |

2025-07-01 |

|

專利讓與 |

一、依據國科會中華民國113年01月03日科部產字第1130001031號函辦理。 二、依據本校第406次智慧財產權審議委員會辦理。 三、公告日:2025年07月01日(星期二) 四、公告讓與期間:自公告日起3個月。 五、敬請有興趣辦理受讓之廠商,或對受讓申請程序有任何疑問者,聯繫研發處技術推廣中心洽談,電話:05-2720411轉16501、16505。 |

||

|

本校案號 |

P105022A |

||

|

專利名稱 |

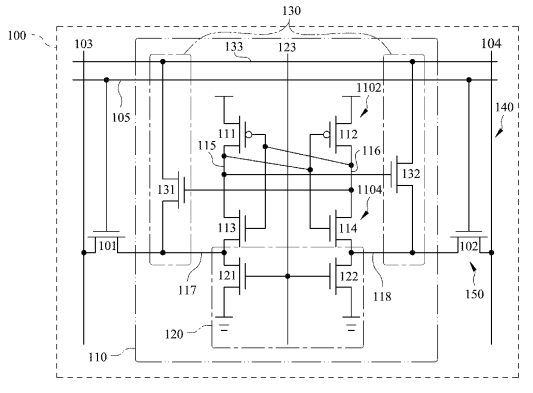

靜態隨機存記憶體細胞元陣列、靜態隨機存取記憶體細胞元及其操作方法「STATIC RANDOM ACCESS MEMORY CELL ARRAY, STATIC RANDOM ACCESS MEMORY CELL AND OPERATING METHOD THEREOF」 |

||

|

發明人 |

王進賢、簡永溱 |

||

|

所屬院 |

工學院 |

提案單位 |

晶片系統研究中心 |

|

類型 |

發明 |

專利權人 |

國立中正大學 |

|

申請號 |

15/655,914 |

申請日期 |

2017-07-21 |

|

公開號 |

US 20180261277 A1 |

公開日期 |

2018-09-13 |

|

證書號 |

US 10,127,976 B2 |

核准日期 |

2018-11-13 |

|

國際分類號 |

G11C-011/00(2006.01);G11C-011/419(2006.01) |

||

|

專利權期間 |

2017.07.21~2037.07.21(延長15天至2037.08.05) |

||

|

專利摘要 |

A static random access memory cell includes a controlling signal line unit, a latch and an access transistor unit. The first bottom transistor unit is controlled by the controlling signal line unit to change voltage levels of the first pseudo node and the second pseudo node. The second bottom transistor unit is controlled by the first internal node to perform connection and disconnection between the controlling signal line unit and the second pseudo node, and the second bottom transistor unit is controlled by the second internal node to perform connection and disconnection between the controlling signal line unit and the first pseudo node. The access transistor unit is controlled by the controlling signal line unit to perform connection and disconnection between the controlling signal line unit, the first pseudo node and the second pseudo node. |

||

|

圖示 |

|||